# **Digital Adder And Subtracter**

# Shih-Ping Hu

Department of Mechanical Engineering Hungkuo Delin University of Technology New Taipei City, Taiwan, Republic of China hushihping@yahoo.com.tw

Abstract—During the period of technology developed and powerful computer, even though traditional instruments of analogy have their indelible merits, but digital instruments are the largest power of impetus advance in technology. The objective of this research paper is to learn how to transfer analogy adders and subtracters into digital adders and subtracters.

Keywords—Digital instrument, Adders and sutracter

# I. Introduction

R<sub>1</sub> 15 ∀ V٥ OPA 15

(1) The full adder of analogy type is shown as fig.(1)

fig.(1) full adder and subtracter of analogy

If the arrangement satisfy

$$\left(\frac{R_{f}}{R_{1}}+\frac{R_{f}}{R_{2}}+\frac{R_{f}}{R_{n}}\right)=\left(\frac{R_{f}'}{R_{1}'}+\frac{R_{f}'}{R_{2}'}+.+\frac{R_{f}'}{R_{m}'}\right)$$

, then,

the output voltage can be got

$$V_0 = \left(\frac{R'_f}{R'_1}v'_1 + \frac{R'_f}{R'_2}v'_2 + \cdot + \frac{R'_f}{R'_m}v'_m\right) - \frac{1}{2}$$

$$(\frac{R_{f}}{R_{1}}v_{1} + \frac{R_{f}}{R_{2}}v_{2} + . + \frac{R_{f}}{R_{n}}v_{n})$$

----(1)

(2)In figure(1), the symbol "OPA" is denoted as operation amplifier, the symbol "V<sub>0</sub>" is denoted as the output voltage, the symbol "R" is denoted as resistance

#### **II. Principle:**

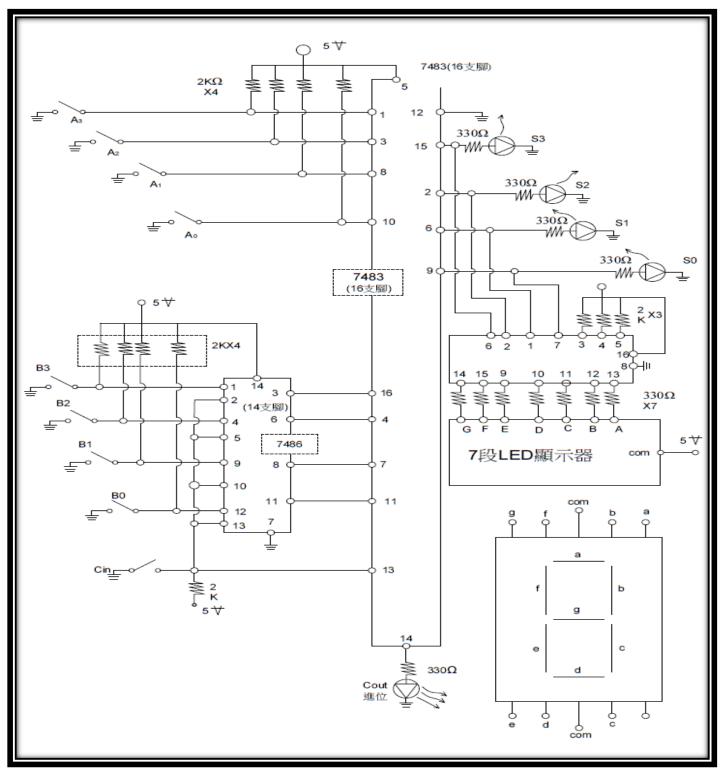

(1)Electronic components in this research paper have ①logic IC 74LS47\*1、74LS83 \*1 and 74LS86\*1 2 resistance  $2k\Omega(1/4W)$ \*12 、 330Ω(1/4W)\*12 ③3-point 2- segment sliding switch\*1 ④ common anode seven-segment LED displayer (small type)  $(\overline{5})$ LED light\*5  $(\widehat{6})$ circuit board\*1(No.:EIC-1106)

The power supply used in this paper need 5 (2) voltages only. We can get from power supply of direct current easily.

(3) The performance of logic IC7486 is to input addend numbers (subtrahend numbers) of the binary B to the system. Its internal structures are XOR gate.

The performance of logic IC7483 is to input passive addend numbers (minuend numbers) of the binary A to the system, then, plus passive addend numbers (minuend numbers) А and addend number (subtrahend numbers) B. Logic IC can output the final numbers eventually.

(5)The performance of logic IC7447 is to transfer the combination result of A plus B into various driving signals to actuate the seven-segment LED displayer.

(6)The performance of common anode seven segment LED displayer is to express the combination

result by the acceptable number of the human(Arabic numbers 1, 2, 3, 4.)

(7)The overall wiring diagram is shown as fig.(2).

fig.(2)the overall wiring diagram.

III. principle explanation of the individual component

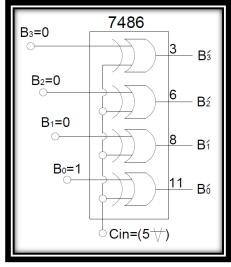

(1) The performance of IC7486 is to input the signal of binary.  $B_3B_2B_1B_0 = 0001_{(2)} = 1_{(10)}$ . Where  $B_0 = 1$  is denoted as 5 voltage,  $B_1 = 0$  is denoted as grounded (0 voltage)

Fig.(3)principle of IC7486

$B_3$ '=0 $\oplus$ 1=1(supplemental number of  $B_3$ )

$B_2$ '=0 $\oplus$ 1=1(supplemental number of  $B_2$ )

$B_1$ '=0 $\oplus$ 1=1(supplemental number of  $B_1$ )

$B_0$ '=1 $\oplus$ 1=0(supplemental number of  $B_0$ )

When  $C_{in}=1$ ; therefore, this paper is treated as the subtracter. On the other hand; when  $C_{in}=0$ ; therefore, this paper is treated as the subtracter.

(2) The performance of  $C_{in}$  is to change the positive & negative mark of addend numbers of B(binary).

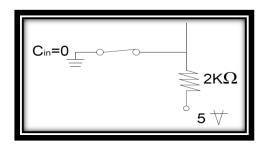

(3)  $C_{in}=0$  ( $C_{in}$  is used to be short circuit) (grounded), then, this paper is a adder shown as figure(4). B' =B  $\oplus 0 = \overline{B} * 0+B * \overline{0} = 0+B * 1=B$ (addend numbers are the same)

$$\begin{array}{cccc} A_3 & A_2 \, A_1 & A_0 \\ +)B_3 & B_2 \, B_1 & B_0 \\ \hline S_3 & S_2 \, S_1 & S_0 \end{array}$$

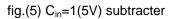

fig.(4) C<sub>in</sub>=0(grounded) adder

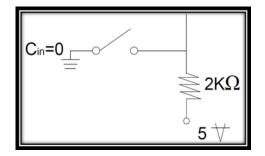

(4)  $C_{in}=1$  ( $C_{in}$  is used to be open loop)(be shut down), then, this paper is a subtracter shown as figure(5). B' = B  $\div$  1 =  $\overline{B} * 1 + B * \overline{1} = \overline{B} + B * 0 = \overline{B}$  (addend numbers are opposite) (supplemental numbers)

$$\begin{array}{cccc} A_{3} & A_{2} & A_{1} & A_{0} \\ \underline{+)B'_{3}} & B_{2}' & B_{1}, & B_{0}' \\ \hline \\ A_{3} & A_{2} & A_{1} & A_{0} \\ \hline \\ \underline{-)B_{3}} & B_{2} & B_{1} & B_{0} \\ \hline \\ \hline \\ S_{3} & S_{2} & S_{1} & S_{0} \end{array}$$

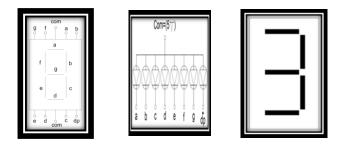

(5) Because the common point of seven segment LED displayers are connected to 5V(anode); therefore, it is called the common anode seven-segment LED displayers shown as figure(6).

.(6)LED displayer show number 3, when a=b=c=d=g=0(V)

(6) In fig.(6), All positive ends of LED displayers are connected to high potential( 5V) together. If any contact of a, b, c, d, e, f, g antennas is connected to low potential(0 V)(grounded); then, the LED displayer will be lighted. [example]: when a=b=c=d=g=0(V) (grounded) (low potential); therefore, it can get the lighting number is 3.

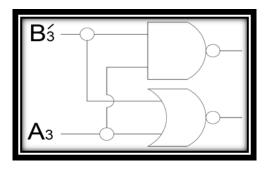

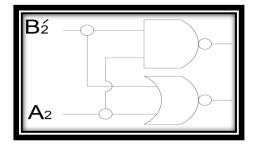

(7)The performance of IC7483 is to input passive addend (or passive subtrahend) numbers (binary)  $A_3A_2A_1A_0{=}1000_{(2)}{=}8_{(10)},$

Where  $A_3=1$  represents high potential (5V),  $A_2=0$ ,  $A_1=0$  and  $A_0=0$  represent low potential (0V) (grounded). This IC combines  $A_3$  and  $B_3$ ' by NAND and NOR gates shown as figure(7). This IC combines  $A_2$  and  $B_2$ ' by NAND and NOR gates shown as figure(8).

fig.(7) A<sub>3</sub> and B<sub>3</sub>' are combined

fig.(8) A2 and B2' are combined

(8)The IC7483 outputs the  $S_3S_2S_1S_0$  to be high potential (5V) after the combination of passive addends (or passive subtrahends)  $A_3A_2A_1A_0$  and addends( or subtrahends)  $B_3B_2B_1B_0$ .

(9)The IC7483 sends the signal of sums ( $S_3S_2S_1S_0$ ) (high potential) to the IC7447

(10)The performance of IC7447 is to transfer the BCD code of sums  $(S_3S_2S_1S_0)$  (high potential) into low potential signals that is essential signals on a, b, c, d, e, f, g of the seven- segment LED displayer

(11)Because the internal circuit of IC7447 is too complex; therefore, this paper would not explain any more **IV. The experimental result (the truth table)**

| No. | Passive<br>addend(subtrahend)<br>numbers A |       |       |       | A<br>(decimal) | Addend(subtrahend)<br>numbers B |                |                |                | B<br>(decimal) | )<br>C <sub>in</sub> | S(sum) |       |                |                | LED<br>displayer |

|-----|--------------------------------------------|-------|-------|-------|----------------|---------------------------------|----------------|----------------|----------------|----------------|----------------------|--------|-------|----------------|----------------|------------------|

|     | $A_3$                                      | $A_2$ | $A_1$ | $A_0$ |                | $B_3$                           | B <sub>2</sub> | B <sub>1</sub> | B <sub>0</sub> |                |                      | $S_3$  | $S_2$ | S <sub>1</sub> | S <sub>0</sub> |                  |

| 1   | 1                                          | 0     | 0     | 0     | 8              | 0                               | 0              | 0              | 1              | 1              | 0(add)               | 1      | 0     | 0              | 1              | 9                |

|     |                                            |       |       |       |                |                                 |                |                |                |                | 1(subtract)          | 0      | 1     | 1              | 1              | 7                |

| 2   | 0                                          | 1     | 0     | 0     | 4              | 0                               | 0              | 0              | 1              | 1              | 0(add)               | 0      | 1     | 0              | 1              | 5                |

|     |                                            |       |       |       |                |                                 |                |                |                |                | 1(subtract)          | 0      | 0     | 1              | 1              | 3                |

| 3   | 0                                          | 1     | 1     | 1     | 7              | 0                               | 0              | 1              | 0              | 2              | 0(add)               | 1      | 0     | 0              | 1              | 9                |

|     |                                            |       |       |       |                |                                 |                |                |                |                | 1(subtract)          | 0      | 1     | 0              | 1              | 5                |

| 4   | 0                                          | 0     | 1     | 1     | 3              | 0                               | 0              | 1              | 1              | 3              | 0(add)               | 0      | 1     | 1              | 0              | 6                |

|     |                                            |       |       |       |                |                                 |                |                |                |                | 1(subtract)          | 0      | 0     | 0              | 0              | 0                |

| 5   | 0                                          | 1     | 1     | 0     | 6              | 0                               | 0              | 0              | 0              | 0              | 0(add)               | 0      | 1     | 1              | 0              | 6                |

|     |                                            |       |       |       |                |                                 |                |                |                |                | 1(subtract)          | 0      | 1     | 1              | 0              | 6                |

Table (1) the truth table

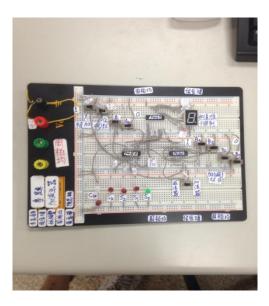

# V. All completed photos:

fig.(9)the completed photograph

# **VI.** Conclusion

(1)The logic IC is composed by some BJT transistors and MOSFET transistors. Its major purpose is simplified the complex circuits of the BJT and the MOSFET to get the same performance. According the operation of this paper, we can certify that the overall wiring diagram is correct unmistakable.

(2)The most complex part of this research paper is logic IC7486 (incompatible gate) (XOR gate). When the "C<sub>in</sub>" is set to zero ( $C_{in}=0$ )(grounded); then, the addend number B and 0 (zero)(grounded) are incompatible each other. In other words, the IC7486 have no performance any more.

(3)When the "C<sub>in</sub>" is set to one ( $C_{in}=1$ ) (5 voltages); then, the addend number B and 1(5 voltages) are incompatible each other. In other words, the IC7486 transfer the addend number B into the supplemental number of B.

# VII. Reference

[1](2001), Exchange Table of the Specification between TTL/IC in the world, (page 64,100,116,162), Taiwan : Chuan Hwa Book Co.LTD

[2]Chang Zianan(2008), '*Digital logic design laboratory*", Book Co. LTD of Taiwan Science and Technology, page167~171, 154~162, first edition, Taiwan, March

[3]Kleitz & William (2008), "*Digital Electronic: A Practical Approach*", Pearson Education, Inc. seventh edition, Chinese Traditional language edition, (2010)

[4]Minzhong Chen (2003), "*The Practice of Digital Logic Circuits*", Super Technology book company Inc., Taiwan, June