# High Speed Convolution And Deconvolution Algorithm Based On Ancient Indian Vedic Mathematics

#### Priya Lad

Electronics And Telecommunication, SIPNA C.O.E.T/ SGBAU University, Amravati (Maharashtra State), India. priyalad3@gmail.com

#### Dr. A.A.Gurjar

Professor, Electronics And Telecommunication, SIPNA C.O.E.T/ SGBAU University Amravati (Maharashtra State), India

Abstract— Convolution and Deconvolution is having wide area of application in Digital Signal Processing. Convolution helps to estimate the output of a system with arbitrary input, with knowledge of impulse response of the system. Linear systems characteristics are completely specified by the systems impulse response, as governed by the mathematics of convolution. And with the knowledge of impulse response and output of a system we recover the unknown input in Deconvolution operation. Convolution and deconvolution is central to many applications of Digital Signal Processing and Image Processing. In DSP the convolution and deconvolution with a long sequence is ubiquitous in many application areas and they consume much of time. Primary requirement of any application to work fast is that increase the speed of their basic building block. Multiplier and Divider is the heart of convolution and deconvolution respectively. It is most important but, slowest unit of the system and consumes much time in the system. Many methods are invented to improve the speed of the multiplier and divider, amongst all vedic multiplier and divider is under focus because of faster working and low power consumption. In this project we have implemented the high speed convolution and deconvolution system using vedic mathematics.

Keywords—Convolution, Deconvolution, Vedic Mathematics , VHDL

#### I. INTRODUCTION

With the latest advancement of technology, digital signal processing plays a pivotal role in many areas of electrical and electronics engineering. High speed convolution deconvolution is central to many applications of Digital Signal Processing and Image Processing, Convolution and Deconvolution having extreme importance in Digital signal processing. Convolution is having wide area of application like designing the digital filter, correlation etc. However it is quite difficult for the new candidate to perform convolution and deconvolution as convolution and deconvolution method is so lengthy and time consuming, beginners often struggle with convolution and deconvolution because the concept and computation requires a number of steps that are tedious and slow to perform. Many methods are proposed for performing convolution, one of a tough approach is a Graphical method, it is quite sophisticated and systematic but, it is very lengthy and time consuming.

Therefore many of the researchers have been trying to improve performance parameters of convolution and deconvolution system using new algorithms and hardware. Complexity and excess time consumption are always the major concern of engineers which motivates them to focus on more advance and simpler techniques. Pierre and John have implemented a fast method for computing linear convolution. This method is similar to multiplication of two decimal numbers and this similarity makes this method easy to learn and quick to compute. Also to compute deconvolution of two finite length sequences, a novel method is used. This method is similar to computing long-hand division and polynomial division. Principal components required for implementation of convolution calculation are adder and multiplier for partial multiplication. Therefore the partial multiplication and addition are bottleneck in deciding the overall speed of the convolution As adder is also an implementation technique. important block for the proposed method, so all required possible adders are studied. Adders which have the highest speed and occupy a comparatively less area, are selected for implementing convolution. Since the execution time in most DSP algorithms depends upon the time required for multiplication, so there is a need of high speed multiplier. Now a days, time required in multiplication process is still the dominant factor in determining the instruction cycle time of a DSP chip. Traditionally shift and add algorithm is being used for designing. However this is not suitable for VLSI implementation and also from delay point of view. Some of the important algorithms proposed in literature for VLSI implementable fast multiplication are Booth multiplier, array multiplier and Wallace tree multiplier. Although these multiplication techniques have been effective over conventional "shift and add" technique but their

disadvantage of time consumption has not been implemented in many completely removed. implemented in many applications such

Vedic Mathematics provides unique solution for this problem. The Urdhva-Tiryagbhyam Sutra or vertically and crosswise algorithm for multiplication is discussed and then used to develop digital multiplier architecture. For division, different division algorithms are studied, by comparing drawbacks and advantages of each algorithm, Paravartya Algorithm based on Vedic mathematics is modified according to need and then used. Many engineering application areas use this Vedic Mathematics, especially in processing. It describes 16 sutras and sub-sutras which cover all the branches of mathematics such as arithmetic, algebra, geometry, trigonometry, statistics etc. Implementation of these algorithms in processors has found out to be advantageous in terms of reduction in power and area along with considerable increase in speed requirements. These Sutras are given in Vedas centuries ago. To be specific, these sutras are described in ATHARVA-VEDA. The sutras and sub-sutras were reintroduced to the world by Swami Bharati Krishna Tirthaji Maharaja in the form of book Vedic Mathematics.

#### II. RELATED WORK

G. Ramanjaneya Reddy and A. Srinivasulu [1] presented convolution process using hardware computing and implementations of discrete linear convolution of two finite length sequences (NXN). This implementation method is realized by simplifying the convolution building blocks. The purpose of this analysis is to prove the feasibility of an FPGA that performs a convolution on an acquired image in real time. The proposed implementation uses a changed hierarchical design approach, which efficiently and accurately quickens computation. The efficiency of the proposed convolution circuit is tested by embedding it during a prime level FPGA. It additionally provides the required modularity, expandability, and regularity to form different convolutions. This particular model has the advantage of being fine tuned for signal processing: in this case it uses the mean squared error measurement and objective measures of enhancement to achieve a more effective signal processing model. They have coded their design using the Verilog hardware description language and have synthesized it for FPGA products using ISE, Modelsim and DC compiler for other processor usage.

Mohammed Hasmat Ali, Anil Kumar Sahani [2], presented the detailed study of different multipliers based on Array Multiplier, Constant coefficient multiplication (KCM) and multiplication based on vedic mathematics. Multiplication-based operations such as Multiply and Accumulate(MAC) and inner product are among some of the frequently used Computation Intensive Arithmetic Functions(CIAF) currently

implemented in many Digital Signal Processing (DSP) applications such as convolution, Fast Fourier Transform(FFT), filtering and ALU in microprocessors. Since multiplication dominates the execution time of most DSP algorithms, so there is a need of high speed multiplier. All these multipliers are coded in Verilog HDL (Hardware Description Language) and simulated in ModelSimXEIII6.4b and synthesized in EDA tool Xilinx ISE12.As multiplication dominates the execution time of the most Digital Signal Processing algorithms, so there is a need of high speed multiplier. The demand for high speed processing has been increasing as a result of expanding computer and signal processing applications. Higher throughput arithmetic operations are important to achieve the desired performance in many real-time signal and image processing applications. One of the key arithmetic operations in such applications is multiplication development of fast multiplier circuit has been a subject of interest over decades. This paper presented the study of different multipliers.

Madhura Tilak [3], presented a novel method of implementing linear convolution of two finite length sequences (N×N) in hardware using hardware description language (VHDL). In this paper, an optimized design for linear convolution is presented. This design model has advavantage of fine tuning depending on the requirement for enhancing the signal processing model. The efficiency of the proposed algorithm is tested by simulations and comparisons with different design approaches using XILLINX software. The efficiency of the proposed algorithm is tested by simulations and comparisons with different design approaches. The proposed circuit is also modular, expandable and regular which provides flexibility. The proposed system design is coded using VHDL language and synthesized for FPGA products with XILLINX 13.1 software.

Abdulqadir Alaqeeli and Janusz Starzyk [4], presented substitute algorithm for calculating the convolution that requires less computation time. The algorithm uses Walsh transform instead of FFTs. FFT based algorithm requires 2 FFTs and one IFFT in addition to complex multiplications and additions. On the other hand, in the Walsh-based method the Walsh transform is required once and there is no multiplications. Therefore, using the Walsh-based algorithm can cut the processing time to about 5 percent of the required time. The additional steps in this algorithm are the permutation of the input samples and the output results. The design uses a field programmable gate array (FPGA) to apply parallel processing concept. This paper presented a design of fast convolver for CDMA signals. This is based on avoiding complex operations such as the ones in FFT-based convolvers. The substitute of the FFT is a binary transform, such as Walsh, that should reduce the operations 3 times because it uses only

real additions. Surprisingly, the used algorithm does not require using the transform more than once. This made the method more efficient. The Walsh function can be transformed into a set of different phase shifts of a single PN sequence using suitable permutations. The convolution can be then performed by reordering the input sequence, performing the Walsh transform, and then permuting the output samples.

Sukhmeet Kaur, Suman and Manpreet Signh Manna [5], proposed implementation of radix-4 Modified Booth Multiplier and this implementation is compared with Radix-2 Booth Multiplier. Modified Booth's algorithm employs both addition and subtraction and also treats positive and negative operands uniformly .No special actions are required for negative numbers. The Speed and Circuit Complexity is compared, Radix-4 Booth Multiplier is giving higher speed as compared to Radix-2 Booth Multiplier and Circuit Complexity is also less as compared to it.

Rashmi K. Lomte (Mrs.Rashmi R. Kulkarni), Prof.Bhaskar P.C [6], proposed a novel method for computing deconvolution of two finite length sequences. In this paper for division, different division algorithms are studied, by comparing drawbacks and advantages of each algorithm, non-restoring algorithm is modified and used. The efficiency of the proposed deconvolution circuit is tested by embedding it on Spartan 3E FPGA. It also provides the necessary modularity, expandability, and regularity to form different deconvolution for any number of bits. It optimized implementation presented an deconvolution. This particular model has advantage of being fine tuned for signal processing. To accurately analyze their proposed system, they have coded our design using the VHDL hardware description language and have synthesized it for FPGA products using ISE.

Honey Durga Tiwari, Ganzorig Gankhuyag, Chan Mo Kim, Yong Beom Cho [7] described new multiplier and square architecture was proposed based on algorithm of ancient indian vedic Mathematics, for low power applications. It is based on generating all partial products and their sums in one step. The design implementation on ALTERA Cyclone—II FPGA shows that the proposed vedic multiplier and square are faster than array multiplier and Booth multiplier. The proposed system design is coded using VHDL language and synthesized for FPGA products with ALTERA Cyclone—II software.

Ritupriya Jha, Ranbir Kumar Paul [8], presented the FPGA comparison, delay and frequency analysis of proposed approximate MAC Unit. The paper's main focus was to analyze fast adder algorithms and multiplication schemes, and utilizes them in the design

and implementation of a MAC unit. Major important issue in digital circuits besides speed, area, power consumption is accuracy. In this work, main focus is on performance and accuracy, but we do provide some numbers for the arithmetic units relating to energy and power. This is to provide an estimate of the amount of energy and power consumed by the units we choose to implement. The priorities of paper in order of importance, are. Robust and safe circuits. Design time, Area/speed balance. Here a new approximate Multiplier technique is proposed whose the lsb four bits are approximated. The proposed approximate and Accurate multiplier and adder and multiply and accumulate unit are designed on Xillinx FPGA Virtex 6 device and analyzed the results. The proposed MAC Unit provides an accuracy of the overall area and Delay and Frequency analysis are presented and compared. This paper explores and analyzes fast adder algorithms and multiplication schemes, and utilizes them in the design and implementation of a MAC unit.

#### III. PROPOSED WORK

#### A. Convolution:

Convolution is considered to be heart of the digital signal processing. It is the mathematical way of combining two signals to obtain a third signal. Convolution helps to estimate the output of a system with arbitrary input, with knowledge of impulse response of the system. Linear systems characteristics are completely specified by the systems impulse response, as governed by the mathematics of convolution. Convolution is an operation which takes two functions as input, and produces a single function output (much like addition or multiplication of functions). Consider two finite length sequences f(n) and h(n) on which the convolution operation is to be performed with lengths I and m respectively. The output of convolution operation y(n) contains I+m-1 number of samples.

The linear convolution of f(n) and h(n) is given by :

$$y(n) = x(n) * h(n)$$

(1)

$$y[n] = \sum_{k=-\infty}^{\infty} x(k)h(n-k)$$

(2)

#### B. Deconvolution:

If the impulse response and the output of a system are known, then the procedure to obtain the unknown input is referred to as deconvolution. The concept of deconvolution is also widely used in the techniques of signal processing and image processing. In general, the object of deconvolution is

to find the solution of a convolution equation of the form:

$$x * h = y$$

Usually, y is some recorded signal, and x is some signal that wish to recover, but has been convolved with some other signal h before get recorded. The function h might represent the transfer function of an instrument or a driving force that was applied to a physical system. If one Know h or at least form of h, then one can perform deterministic deconvolution.

If the two sequences x(n) and h(n) are causal, then the convolution sum is

$$y[n] = \sum_{k=0}^{n} x(k)h(n-k)$$

Therefore, solving for x(n) given h(n) and y(n) results in

$$x(n) = \frac{y(n) - \sum_{k=0}^{n-1} x(k)h(n-k)}{h(n)}$$

Where

$$x(0) = \frac{y(0)}{h(0)}$$

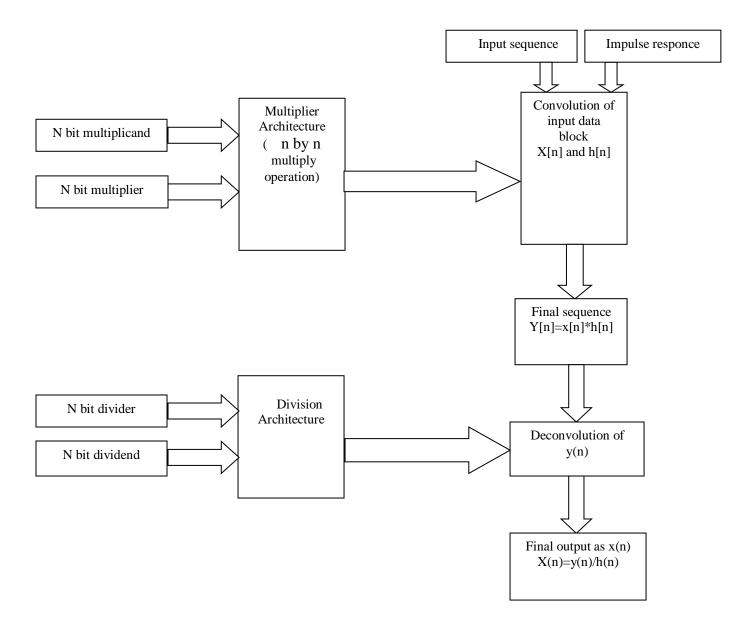

# C. Block Diagram

A block diagram of proposed system is shown in Figure 2. It consists of multiplier based on vedic sutra i.e.Urdhva-Tiryagbhyam that are embedded into convolution of two finite sequence and vedic divider that are embedded in deconvolution process to recover the original data. System block diagram is shown in Figure 2.

Primary requirement of any application to work fast is that increase the speed of their basic building block. Multiplier and Divider is the heart of convolution and deconvolution respectively as shown in above fig. It is most important but, slowest unit of the system and consumes much time in the system. Many methods are invented to improve the speed of the Multiplier and Divider, amongst all Vedic Multiplier and Divider is under focus because, of faster working and low power consumption. In this project the speed of Convolution and Deconvolution module is improved using Vedic multiplier and Divider. It consists of multiplier based on vedic sutra i.e. URDHVA Tiryagbhyam that are embedded into convolution of two finite sequence and divider based on Vedic sutra Paravartya Sutra that are embedded in deconvolution process to recover the original data.

# D. Conventional multiplier.

An array multiplier is a digital combinational circuit that is used for the multiplication of two binary

numbers by employing an array of full adders and half adders. This array is used for the nearly simultaneous addition of the various product terms involved. To form the various product terms, an array of AND gates is used before the Adder array.

To clarify more on the concept, let us consider a  $4\times4$  bit multiplication with A and B being the multiplicand and the multiplier respectively. Assuming A =  $(1\ 0\ 0\ 1)$  and B=  $(1\ 0\ 1\ 0)$ , the various bits of the final product can be written as:-

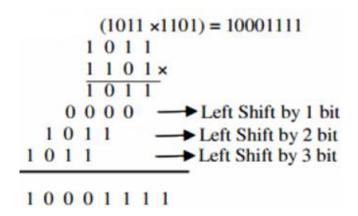

Fig.1: Example of conventional multiplier

For the above multiplication, an array of sixteen AND gates is required to form the various product terms and an Adder array is required to calculate the sums involving the various product terms and carry combinations in order to get the final Product bits.

The Hardware requirement for an m x n bit array multiplier is given as:-

(m x n) AND gates,

(m-1).n Adders in which n HA(Half Adders) and (m-2).n FA(full adders).

Here from the above example it is inferred that partial products are generated sequentially, which reduces the speed of the multiplier. However the structure of the multiplier is regular. Also, in multiplier worst case delay would be (2n+1) td. Multiplier gives more power consumption as well as optimum number of components required, but delay for this multiplier is larger. It also requires larger number of gates because of which area is also increased; due to this multiplier is less economical.

3238

Fig.2: SYSTEM BLOCK DIAGRAM

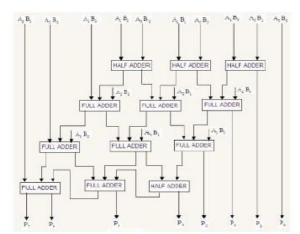

Consider 4x4 multiplications, say A= A3 A2 A1 A0 and B= B3 B2 B1 B0. The output line for this multiplication is P7 P6 P5P4P3P2 P1 P0. Using the fundamental of Array Multiplication, taking partial product addition is carried out in Carry save form; we can have the following structure for multiplication as shown in Figure 3.

Fig.3: Structure for conventional multiplier

Urdhva Tiryagbhyam Sutra is a general multiplication formula applicable to all cases of multiplication. It literally means "Vertically and crosswise". It is based on a novel concept through which the generation of all partial products can be done with the concurrent addition of these partial products. Since the partial products and their sums are calculated in parallel, the multiplier is independent of the clock frequency of the processor. Thus the multiplier will require the same amount of time to calculate the product and hence is independent of the clock frequency. The net advantage is that it reduces the need of microprocessors to operate at increasingly high clock frequencies. While a higher clock frequency generally increased results processing power, in disadvantage is that it also increases power dissipation which results in higher device operating temperatures. By adopting the Vedic multiplier, microprocessors designers can easily circumvent problems to avoid catastrophic device failures. Due to its regular structure, it can be easily layout in a silicon chip. The Multiplier has the advantage that as the number of bits increases, gate delay and area increases very slowly as compared to other multipliers. Therefore it is time, space and power efficient. The main advantage of the Multiplication algorithm (Urdhva Tiryagbhyam Sutra) stems from the fact that it can be easily implemented in FPGA due to its simplicity and regularity.

# E. Vedic Multiplier

Vedic mathematics is part of four Vedas (books of wisdom). It is part of Sthapatya-Veda (book on civil engineering and architecture), which is an upa-veda (supplement) of Atharva Veda. It gives explanation of several mathematical terms including arithmetic, geometry (plane, co-ordinate), trigonometry, quadratic equations, factorization and even calculus. His Holiness Jagadguru Shankaracharya Bharati Krishna Teerthaji Maharaja (1884-1960) comprised all this work together and gave its mathematical explanation while discussing it for various applications. The sutras and sub-sutras were reintroduced to the world by Swami Bharati Krishna Tirthaji Maharaja in the form of book Vedic M Ancient Indian.

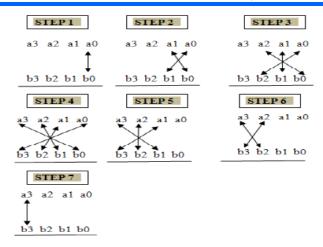

The work presented here, makes use of Vedic Mathematics. "Urdhva Tiryagbhyam Sutra" or "Vertically and Crosswise Algorithm" of Vedic mathematics for multiplication is used to develop digital multiplier architecture. The multiplication of two 4 bit number using Urdhva Tiryagbhyam is shown in figure 4.

**Fig.4:** Multiplication of two 4 bit numbers using Urdhva Tiryagbhyam method

Thus, the product terms can be calculated as

A1=a0\*b0 A2=a0\*b1+a1\*b0+prevcarry A3=a0\*b2+a1\*b1+a2\*b0+prevcarry A4=a0\*b3+a1\*b2+a2\*b1+a3\*b0+prevcarry A5=a1\*b3+a2\*b2+a3\*b1+prevcarry A6=a2\*b3+a3\*b2 + prevcarry A7=a3\*b3+ prevcarry

After comparative study of conventional multipliers and vedic multiplier, Urdhva Tiryagbhyam sutra is shown to be an efficient multiplication algorithm. Therefore we are using vedic multiplier in convolution system to improve its performance.

#### F. Proposed Convolution:

The linear convolution of x(n) and h(n) is y(n) =g(n). This can be solved by several methods, resulting in the sequence y(n). In this approach for calculating the convolution sum is set up like multiplication (except carries are not performed out of a column). where the convolution of x(n) and h(n) is performed as shown in fig. 5.5. To get convolution of two sequences, where each sequence consist of 4 samples, sixteen partial products are calculated and afterwards they are added to get convolution sequence y[n]. In this paper, Partial products are calculated by using vedic multiplier based on Urdhva Tiryagbhyam algorithm. Here to minimize hardware, width of each input sample is restricted to 4 bit. Hence maximum possible input sample value would be (1111)2 or (15)10 or (F) h. Multiplier required is 4×4 bit. Each multiplier gives 8 bit long partial product. Convolution outputs y[6] and y[0] are direct Partial products. While remaining obtained after addition of intermediate partial products.

Let two discrete length sequences are x[n] and h[n].Where  $x[n] = \{x3 \ x2 \ x1 \ x0\}$  and  $h[n] = \{h3 \ h2 \ h1 \ h0\}$  are convolved. As each sample is four bit long ,each partial product is eight bit long e.g. x0h0, x3h0, x3h3 all are eight bit long. y[n] = x[n] \* h[n], in a way

as mentioned above. Procedure is rearranged as shown in figure 5.

| x[n] |            |      | x3   | <b>x</b> 2 | x1   | x0   |   |

|------|------------|------|------|------------|------|------|---|

|      | ×          |      |      |            |      |      |   |

| h[n] |            |      | h3   | h2         | h1   | h0   |   |

|      |            |      | x3h0 | x2h0       | x1h0 | x0h0 | _ |

|      |            | x3h1 | x2h1 | x1h1       | x0h1 |      |   |

|      | x3h2       | x2h2 | x1h2 | x0h2       |      |      |   |

| x3h3 | x2h3       | x1h3 | x0h3 |            |      |      |   |

| Y6   | <b>Y</b> 5 | Y4   | Y3   | <b>Y</b> 2 | Y1   | Y0   |   |

**Fig.5:** Convolution of x[n] and h[n]

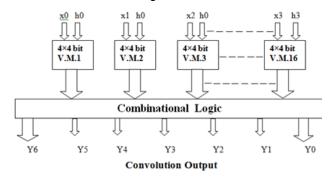

In propose system to generate sixteen partial products, sixteen vedic multipliers are used and to perform further operations of addition, all the outputs are latched as shown in figure.6.

Fig.6: Block Diagram for convolution

As shown in figure 6, 4 bit long samples are applied to 4X4 bit vedic multipliers (V.M.). Output of each Vedic multiplier is 8 bit long partial product. Vedic multiplier uses Urdhva Tiryagbhyam algorithm for multiplication. In parallel processing, to generate sixteen partial products, sixteen Vedic multipliers are used to boost speed. To perform further operation of addition, all outputs are latched. And corresponding output Y0, Y1, Y2, Y3, Y4, Y5 and Y6 are produced. Maximum possible length of Y0 and Y6 is 8 bit, while of Y1 toY5 is 9 bit. The design is built in VHDL and implemented on an EPGA.

# G. Conventional divider:

Division is most complex and very time consuming if it is done straight forwardly, because we need to compare the remainder with the divisor after

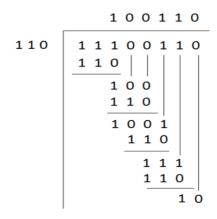

subtraction.Basically division algorithm is every subtractive multiplicative and classified as approaches. Multiplicative division algorithms do not compute the quotient directly, but use successive approximations to converge to the quotient. Normally, such algorithms only yield a quotient, but with an additional step the final remainder can be computed, if needed. Consider the following example, Assuming A=(11100110) and B=(110)

#### Example:

Fig.7: Example of conventional divider

Division is always considered to be bulky and one of the most difficult operations in arithmetic and hence all the implementations of division algorithms in VLSI architecture have higher orders of time and space complexities. Vedic Mathematics on the other hand offers a new holistic approach to mathematics.

# H. Vedic Divider:

The word "Vedic" is derived from the word "Veda" which means the store-house of all knowledge. Vedic mathematics is mainly based on sixteen sutras & from that paravartya sutra is for division. Sanskrit term PARAYARTYA means all Transpose and apply. In this project a systematic method is used for division which based on Paravartya Sutra. Paravartya Sutra help to minimize computation and maintain accuracy even as the number of iteration is reduced. It provides easier and logically simple implementation.

According to paravartya sutra, all the digit of the divisor is complemented except the most significant digit. This complemented digit is initially multiplied with the most significant digit of the dividend and this multiplication result is added with columns of dividend. The result of addition is again multiplied with complemented digits of Divisor and added with the remaining column of the dividend, followed successive multiplication and addition of consecutive column. The summation of all columns results forms quotient and remainder. Implementation of the algorithm is illustrated using an example. Assume the dividend is 1111 and divisor is 101. The

division of this two numbers using paravartya sutra is shown in figure 8.

Example

| Divisor |     |    | Dividend    |    |       |         |

|---------|-----|----|-------------|----|-------|---------|

| 1       | 0   | 1  | 1           | 1  | 1     | 1       |

|         | - 0 | -1 |             | -0 | -1    |         |

|         |     |    |             |    | -0    | -1      |

|         |     |    | 1           | 1  | 0     | 0       |

|         |     |    | Quotient=11 |    | Remai | nder=00 |

Fig.8: Division using paravartya sutra

In the proposed work we are optimizing the process of multiplication and complement ,addition in the paravartya sutra to ANDing and substraction method respectively. Thus the above example can be written as

|   | Divisor |   |     | Di       | vidend |         |

|---|---------|---|-----|----------|--------|---------|

| 1 | 0       | 1 | 1   | 1        | 1      | 1       |

|   | 0       | 1 |     | 0        | 1      |         |

|   |         |   |     |          | 0      | 1       |

|   |         |   | 1   | 1        | 0      | 0       |

|   |         |   | Quo | tient=11 | Remai  | nder=00 |

Fig 9: Optimization in paravartya sutra

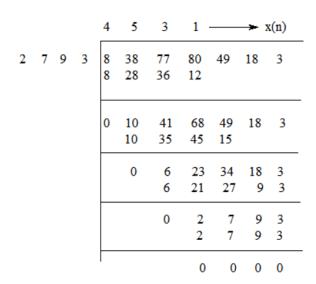

#### I. Proposed Deconvolution:

The linear deconvolution of two finite length sequences can be solved by several method, in this approach for calculating the deconvolution , deconvolution operation is set up like long-hand division and polynomial division , just as the propose convolution method is similar to multiplication. In this approach division operation is implemented by using Paravartya algorithm based on vedic mathematics while to obtain partial products vedic multiplier is used.

To illustrate the method Consider the example 2, let Y(n) be the convolved sequence equal to (8,38,77,80,49,18,3) and h(n) be the finite length sequence equal to (2,7,9,3).

Fig.10: Proposed Deconvolution

In the above method division 8/2,10/2,6/3,2/2 is carried out using above paravartya sutra and multiplication of 4\*2,4\*7, 4\*9,4\*3 and so on are carried out using vedic multiplier to recover the input sequence  $x(n)=(4\ 5\ 3\ 1)$ .

#### IV. RESULT & DISCUSSION

This chapter presents the test environment and the experimental results of design modules. The objectives of this project are to design and implement the Vedic multiplier and divider architecture in convolution and deconvolution respectively to improve speed performance and, reduction area, power .The design is implemented in VHDL, simulated using Modelsim and synthesized by Altera Quartus II.

## A. Simulation of Convolution:

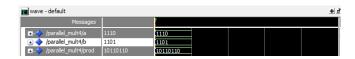

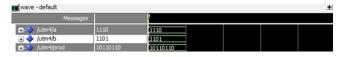

The multiplier is simulated on Modelsim simulator. The figure 10 shows the simulation result of multiplier. a and b are the inputs of 4 bit each and prod gives multiplication result.

The simulated result of conventional multiplier is shown below

Fig. 10: Simulation of multiplier.

The Vedic multiplier is simulated on Modelsim simulator. The figure 11 shows the simulation result of Vedic multiplier. a and b are the

inputs of 4 bit each and prod gives multiplication result based on urdhva- tiryagbhyam.

The simulated result of Vedic multiplier is shown below

Fig.11: Simulation of Vedic multiplier.

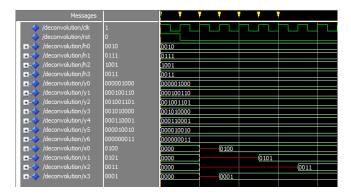

The Convolution module is simulated on Modelsim simulator. The figure 12 shows the simulation result of Convolution module using Vedic Mathematics. A1, A2, A3, A4 and B1, B2, B3, B4 are the inputs of 4 bit each and conv1, conv2, conv3, conv4, conv5, conv6, conv7 are the outputs.

The simulated result of Convolution using Vedic Multiplier is shown below

| Messages                            |           |                     |

|-------------------------------------|-----------|---------------------|

| /convolution/clk                    | 1         |                     |

| /convolution/rst                    | 0         |                     |

| <b>+</b> -<> /convolution/x0        | 0100      | 0100                |

| +> /convolution/x1                  | 0101      | 0101                |

| +> /convolution/x2                  | 0011      | 0011                |

| <b>≖</b> - <b>♦</b> /convolution/x3 | 0001      | 0001                |

| ← /convolution/h0                   | 0010      | 0010                |

| +> /convolution/h1                  | 0111      | 0111                |

|                                     | 1001      | 1001                |

|                                     | 0011      | 0011                |

| +> /convolution/y0                  | 000001000 | 000000000 000001000 |

| +> /convolution/y1                  | 000100110 | 000000000 000100110 |

| +> /convolution/y2                  | 001001101 | 000000000 001001101 |

|                                     | 001010000 | 000000000 001010000 |

|                                     | 000110001 | 000000000 000110001 |

| <b>∓</b> -<> /convolution/y5        | 000010010 | 000000000 000010010 |

| <b>∓</b> - <b>◇</b> /convolution/y6 | 000000011 | 000000000 000000011 |

|                                     |           |                     |

Fig.12: Simulation results of Convolution using Vedic mathematics

# B. Analysis and Synthesis:

The analysis and synthesis of multiplier and divider is done using Altera Quartus II . Analysis shows that Vedic multiplier and divider requires less time and less power. Table 1 shows Timming Analysis using Altera Quartus II Cyclone II for multiplier and vedic multiplier. And Table 2 shows Timming Analysis using Altera Quartus II Cyclone II for multiplier and divider.

Summary:

Table 1: Timming Analysis using Altera Quartus II Cyclone II for multiplier and Vedic multiplier:

| Method                    | Delay     |

|---------------------------|-----------|

| Conventional Multiplier   | 70.678Ns  |

| Proposed Vedic Multiplier | 20.166 Ns |

From the above table of timming analysis of conventional multiplier and vedic multiplier using Altera Quartus II, it can be proved that Vedic multiplier is more efficient than the conventional multiplier in terms of respective paramaters. And vedic multiplier requires very less time compare to conventional multiplier. And hence Convolution using vedic multiplier is more faster than the conventional convolution. Thus the application of this Vedic Multiplier in Convolution Operation provide us the High Speed Convolution which conclude our project.

#### C. Simulation of Deconvolution:

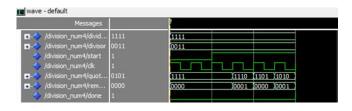

The divider is simulated on Modelsim simulator. The figure 13 shows the simulation result of divider. Dividend and divisor are the inputs of 4 bit each and quot gives division result.

The simulated result of conventional divider is shown below

Fig.13: Simulation of divider

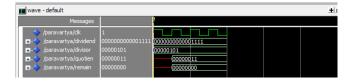

The Vedic divider is simulated on Modelsim simulator. The figure 14 shows the simulation result of Vedic divider. x and y are the inputs of 4 bit each and quot gives division result based on paravartya sutra.

The simulated result of Vedic divider is shown below

Fig.14: Simulation of vedic divider.

The Deconvolution module is simulated on Modelsim simulator. The figure 15 shows the simulation result of Deconvolution module using Vedic Mathematics. y0, y1, y2, y3, y4, y5, y6 and g0, g1, g2, g3 are the inputs of 8 bit each and x0, x1, x2, x3 are the outputs.

The simulated result of Deconvolution using Vedic Divider is shown below

Fig.15: Simulation results of Deconvolution using Vedic mathematics

#### D. Summary:

Table 2: Timming Analysis using Altera Quartus II Cyclone II for divider and Vedic divider:

| Method                 | Delay    |

|------------------------|----------|

| Conventional divider   | 12.897Ns |

| Proposed Vedic divider | 9.625Ns  |

From the above table of timming analysis of conventional divider and vedic divider using Altera Quartus II, it can be proved that Vedic divider is more efficient than the conventional divider in terms of respective paramaters. And vedic divider requires very less time compare to conventional divider. And hence deconvolution using vedic divider is more faster than the conventional deconvolution. Thus the application of this vedic divider in deconvolution operation provide us the high speed deconvolution which conclude our project.

# V.APPLICATION

The main application of such system is in digital image processing as convolution plays an important role in many algorithms in edge detection and related processes.

- It helps in radiotherapy treatment planning systems, where most part of all modern codes of calculation applies a convolution – superposition algorithm.

- Speeding up convolution and deconvolution using a Hardware Description Language for design entry not only increases (improves) the level of abstraction, but also opens new possibilities for using programmable devices.

- Any kind of application where high speed convolution and deconvolution algorithm is needed.

#### VI.Conclusion

This propose system provides a method for calculating the linear convolution and deconvolution with the help of vedic algorithms that is easy to learn and perform. It presents faster implementation of linear convolution and deconvolution. The execution time and area required for propose convolution and deconvolution using vedic multiplication and division respectively compare algorithm with that conventional convolution and deconvolution with the simple multiplication and division is less from the simulated result. The project, presents speedy implementation of linear convolution deconvolution. This particular model has advantage of being fine tuned for any signal processing application. Design is coded using the VHDL hardware description language and synthesized it for FPGA products using quartus2.

#### VII.FUTURE ASPECTS

The proposed design is tested for 4×4 bit convolution and deconvolution using modelsim simulator. The presented concept can be extended on N×N convolution and deconvolution. The modularity and reconfigurability of FPGA makes the design compatible for future improvements. In future this system will become more faster and become more efficient in terms of area, power.

#### VIII.REFERENCES

- [1] J. G. Proakis and D. G. Manolakis, "Digital Signal Processing: Principles, Algorithm, and Applications," 2nd Edition. New York Macmillan, 1992.

- [2] Pierre, John W. "A novel method for calculating the convolution sum of two finite length sequences." Education, IEEE Transactions on 39.1 (1996).

- [3] Rashmi K. Lomte (Mrs.Rashmi R. Kulkarni), Prof.Bhaskar P.C, "High Speed Convolution and Deconvolution Using Urdhva Triyagbhyam". VLSI

- (ISVLSI), 2011 IEEE Computer Society Annual Symposium on. IEEE, 2011.

- [4] Thapliyal, Himanshu, and M. B. Srinivas. "High Speed Efficient NxN Bit Parallel Hierarchical Overlay Multiplier Architecture Based on Ancient Indian Vedic Mathematics." Enformatika Trans 2 (2004): 225-228.

- [5] Senapati, Ratiranjan, Bandan Kumar Bhoi, and Manoranjan Pradhan "Novel binary divider architecture for high speed VLSI applications." Information & Communication Technologies (ICT), 2013 IEEE Conference on. IEEE, 2013.

- [6] Huddar S., Kalpana M., Mohan S."Novel High Speed Vedic Mathematics Multiplier Using Compressors" Automation, Computing, Communication, Control and Compressed Sensing (iMac4s), 2013 International Multi-Conference pp: 465 - 469

- [7] Akhter, Shamim. "VHDL implementation of fast NxN multiplier based on vedic mathematic." In Circuit Theory and Design, 2007. ECCTD 2007. 18th European Conference on, IEEE, 2007.

- [8] Jagadguru Swami Sri Bharati Krisna Tirthaji Maharaja, "Vedic Mathematics: Sixteen Simple Mathematical Formulae from the Veda", Motilal Banarasidas Publishers, Delhi, 2009, pp. 5-45.

- [9] Itawadiya, Akhalesh K., et al. "Design a DSP operations using vedic mathematics" Communications and Signal Processing (ICCSP), 2013 International Conference on, IEEE, 2013.

- [10] L. Sriraman, T.N. Prabakar, "Design and Implementation of Two Variable Multiplier Using KCM and Vedic Mathematics" 1st Int. Conf. on Recent Advances in Information Technology, Dhanbad, India, 2012, IEEE Proc, pp. 782-787.

- [11] Honey Tiwari, Ganzorig ankhuyag, Chan Mo Kim, Yong Beom Cho, "Multiplier design based on ancient Indian Vedic Mathematics", IEEE, 2008 International Soc Design Conference.

- [12] Rudagi, J. M., Vishwanath Ambli, Vishwanath Munavalli, Ravindra Patil, and Vinaykumar Sajjan. "Design and implementation of efficient Multiplier using Vedic mathematics." (2011): 162-166.

- [13] Bansal, Y.; Madhu, C.; Kaur, P." High speed Vedic Multiplier Design A Review" Proceedings of 2014 RAECS UIET Panjab University Chandigarh, 06 08.IEEE March, 2014.

- [14] Jain S., Pancholi M, Garg Harsh, Saini S. "Binary Division algorithm and high speed Deconvolution algorithm (Based on ancient Indian Mathematics)" Electrical Engineering/Electronics, Computer, Telecommunications and Information Technology (ECTI-CON), 2014 11<sup>th</sup> International Conference Page(s): 1 5.

- [15] Pandit Ramnandan Shastri, "Vedic Mathematics", Arihant Publications, p.V.

- [16] Vaidya, Sumit, and Deepak Dandekar. "Delay-Power Performance Comparison of multipliers in VLSI circuit design." International Journal of Computer Networks & Communications (IJCNC) 2.4 (2010): 47-56.

- [17] Thomas Oelsner, "Implementation of Data Convolution Algorithms in FPGAs" <a href="http://www.quicklogic.com/images/appnote18.pdf">http://www.quicklogic.com/images/appnote18.pdf</a>

- [18] Abraham H. Diaz, Domingo Rodriguez, "One Dimentional Cyclic Convolution Algorithms With Minimal Multiplicative Complexity", ICASSP.

- [19] Mountassar Maamoun, "VLSI Design for High Speed Image Computing Using Fast Convolution-Based Discrete Wavelet Transform", Proceedings of the world Congress on Engineering Vol 1, July 2009.

- [20] Very High Speed Integrated Circuit Hardware Description Language. URL: http://electrosofts.com/vhdl/.

- [21] Purushottam D. Chidgupkar and Mangesh T. Karad, "The Implementation of Vedic Algorithms in Digital Signal Processing", Global J. of Engng. Educ., Vol.8, No.2 © 2004 UICEE Published in Australia.

- [22] Shripad Kulkarni, "Discrete Fourier Transform (DFT) by using Vedic Mathematics", report, vedicmathsindia.blogspot.com, 2007

- [23] Alan V. Oppenheim, Ronald W. Schafer with John R. Buck, Discrete Time Signal Processing, Second Edition.