# An Efficient Congestion Aware Adaptive Routing Techniques in Dram

**T.Radhu<sup>1</sup>** PG Scholar<sup>1</sup>, VLSI Design, Sona College of Technology, Salem, India <u>radhu846@gmail.com</u>

Abstract-The power dissipated by systemlevel buses is the largest contribution to the global power of complex VLSI circuits. Therefore, the minimization of the switching activity at the I/O interfaces can provide significant savings on the overall power budget. This paper presents innovative encoding techniques suitable for minimizing the switching activity of system-level address buses. In particular, the schemes such as full inversion, even inversion and odd inversion target the reduction of the average number of bus line transitions per clock cycle. Experimental results, conducted on address streams generated by a real Field Programmable Gate Array (FPGA), have demonstrated the effectiveness of the proposed methods. It can reduce the power consumption and improvement in performance and throughput when compared to existing system.

Keywords—FPGA, power, area, performance, ETI, PaCC.

#### I. INTRODUCTION

More number of non-volatile flip flops and registers are used.it requires more amount of space and energy for power consumption. In existing system processors contain capacitor for easy drain off the power supply .As the system does not requires any external backups. Non-volatile processors require more time to initiate the system and data is erased when supply is OFF and that condition requires more power dissipation.

#### II. OVERVIEW

The processor is implemented for area impact and redundancy problem .lt reduces the average number of bus line transition due to cyclic process.

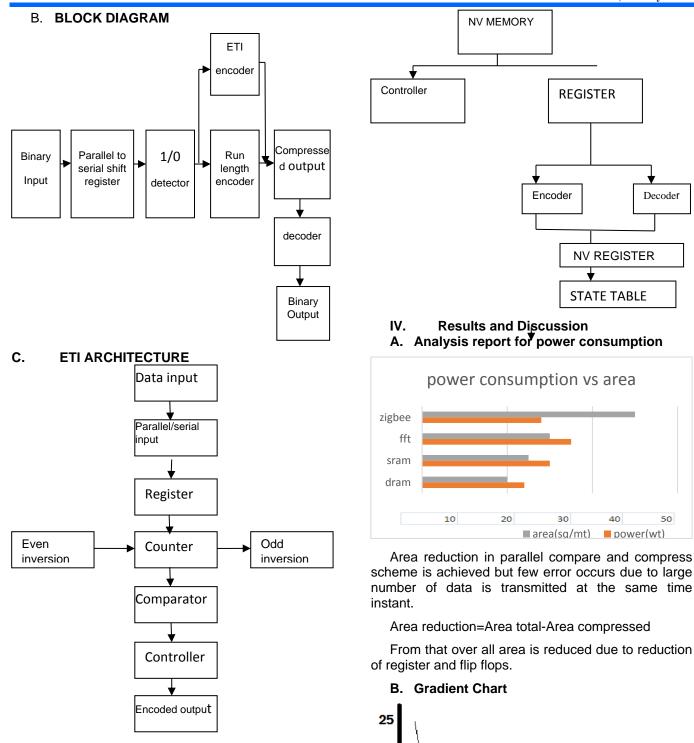

# A. PaCC Design

Generally processor ratio is analysed by using compress and compare scheme .By using this parallel compare and compress scheme, compression ratio of the data level is reduced. But it has a problem due to transmission of data bit into the processor. Due to transmission of large number of data bit into the processor, collision occurs. This problem is rectified in collision avoidance scheme. Here a technique of run length encoder is used to reduce redundancy of the bit level. S.Jayapoorani<sup>2</sup>

Assistant Professor<sup>2</sup>, Sona College of Technology, Salem, India jayapoorani@yahoo.com

# B. Run length encoder(RLE)

A data bit can be reduced from 16k to 2k level.

0

0000 1111 0000 \_\_\_\_\_\_\_\_\_

1

0

By using run length encoding only continuous zero and one can be reduced. If there is a mismatch of bit level 101010 –data bit cannot be compressed by using RLE method. So inversion technique is involved for reducing the data bit level.

#### III. Proposed Method

#### METHOD FOR REDUCING CONGESTION

#### A. Embedded Transition Inversion (ETI) ENCODER

From Embedded Transition Inversion (ETI) encoder four inversion techniques is involved to compress the data bit.

- Full inversion

- Odd inversion

- Even inversion

- Zero inversion

Inversion techniques take place due to compression of data length. For example full inversion requires inverting all one as zero and zero as one.

Even inversion For example 01010101 here even inversion can be take place

In this inversion 1—0(changed) one can be converted to zero. Like that for odd inversion also only odd term of data bit is changed and length of bit level is reduced.

ETI encoder has inversion technique. This technique is used to compress the data bit level. The graphical chart is refer to reduction of the area and power consumption.

#### D. Non-volatile processor

20

15

10

5

0

gradient =

30 AREA (Sq.mt)

14 % bit

450

50

From the evaluation PACC leads to compression of the data bit level. It is implemented in real time system for more memory space and less power consumption. From the chart it is observed that area is reduced to bit level of 14%.

#### C. Area reduction

From PACC method area is compressed by using design compiler. Based on reduction only 23.4% to 27% is reduced .By using an inversion techniques scheme area is reduced up to 33% to 39% .It is efficient and collision problem is reduced.

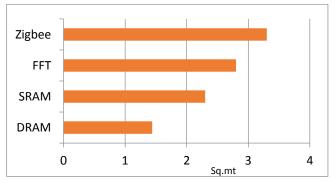

#### D. Area analysis chart

From the chart it is observed that the area is reduced maximum for DRAM and it 1.4 sq meters.

#### E. Codec performance level

The run length encoder and decoder plays role in PaCC method but it is not efficient for reduction of data bit level .So inversion scheme exhibits better performance in reduction of bit level.

100% 80% 60% 40% 20% 0% zigbee FET SRAM DRAM Area

F. Power and area minimization chart

\_\_\_\_ power

Area is minimized up to 33% and power consumption is reduced up to 42% for DRAM.

# V. CONCLUSION

Non Volatile processor reduces power consumption and area size .The cost of chip is also reduced. From advanced codec level of parallel compare and compress scheme it reduces the number of flip flops .According to this technique, power consumption and bit level compression cannot be reduced by using congestion aware techniques .It reduces traffic due to data transmission and glitches is avoided.

Network level data transmission causes congestion problem. It can be avoided by using congestion aware techniques and inversion is used to reduce that data bit level. Area is reduced up to 33% and power consumption is reduced up to 42%.

# VI. Acknowledgment

I express my sincere thanks to SONA college of Technology for providing the components for performing this work.

# VII. REFERENCES

- Y. Wang, Y. Liu, S. Li, D. Zhang, B. Zhao, B. Sai, M.-F. Chiang, Y. Yan, and H. Yang, "A 3us wakeup time nonvolatile processor based on ferroelectric flip-flops," in Proc. ESSCIRC, Sep. 2012, pp. 149–152.

- M. Qazi, A. Amerasekera, and A. P. Chandrakasan, "A 3.4 pJFeRAM- enabled D flipflop in 0.13 μm CMOS for nonvolatile processing in digital systems," in Proc. ISSCC, Feb. 2013, pp. 192–193.

- W. Zhao, E. Belhaire, V. Javerliac, C. Chappert, and B. Dieny, "A non- volatile flip-flop in magnetic FPGA chip," in Proc. DTIS, Sep. 2006, pp. 323– 326.

- N. Sakimura, T. Sugibayashi, R. Nebashi, and N. Kasai, "Nonvolatile magnetic flip-flop for standbypower-free SoCs," IEEE J. Solid-State Circuits, vol. 44, no. 8, pp. 2244–2250, Aug. 2009.

- J. Wang, Y. Liu, H. Yang, and H. Wang, "A compare-and-write Ferro- electric nonvolatile flipflop for energy-harvesting applications," in Proc. ICGCS 2010, pp. 646–650.

- 6. J. Terni, A. Schwarzbacher, B. Hoppe, and K. Noff, "A hardware implementation of a run length encoding compression algorithm with parallel inputs," in Proc. ISSC, Jun. 2008, pp. 337–342.

- G. Beenker and K. Immink, "A generalized method for encoding and decoding run-lengthlimited binary sequences (Corresp.)," IEEE Trans. Inf. Theory, vol. 29, no. 5, pp. 751–754, Sep. 1983.

- Y. Wang, Y. Liu, Y. Liu, D. Zhang, S. Li, B. Sai, M.-F. Chiang, and H. Yang, "A compressionbased area-efficient recovery architecture for nonvolatile processors," in Proc. DATE, Mar. 2012, pp. 1519–1524.

- 9. D. Huffman, "A method for the construction of minimum-redundancy codes," *Proc. IRE*, vol. 40, no. 9, pp. 1098–1101, Sep. 1952.

- 10. Nikkei Electronics Asia. (2008). *Rohm Develops Non-Volatile Register; Slashes Dissipation*,HongKong[Online].Available:<u>http://tec</u>

hon.nikkeibp.co.jp/article/HONSHI/20080729/155 646/

- 11. X. Guo, E. Ipek, and T. Soyata, "Resistive computation: Avoiding the power wall with low-leakage, STT-MRAM based computing," in *Proc.37th Annu. ISCA*, 2010, pp. 371–382.

- 12. M. Poremba and Y. Xie, "NVMain: An architectural-level main memory simulator for emerging non-volatile memories," in *Proc. ISVLSI*, 2012,pp. 392–397.